Github Wisp Rfid Verilog Rfid And Tester In Verilog

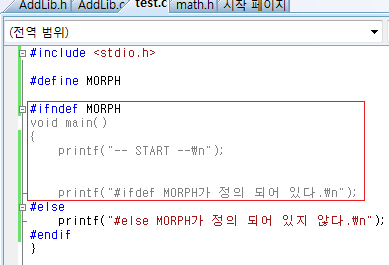

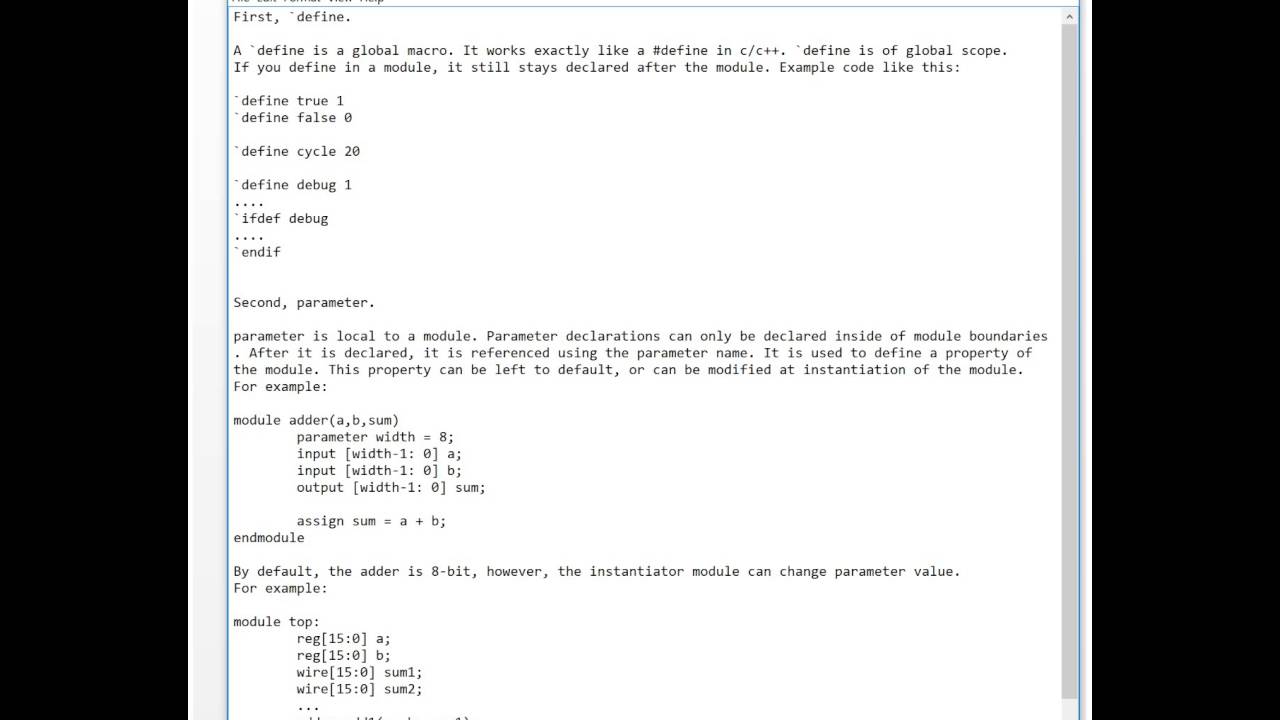

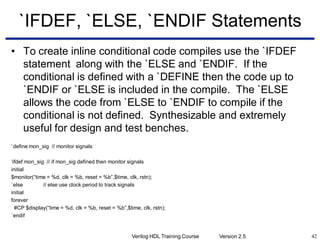

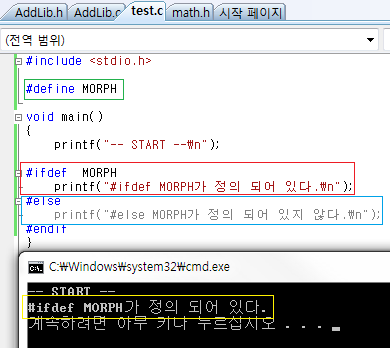

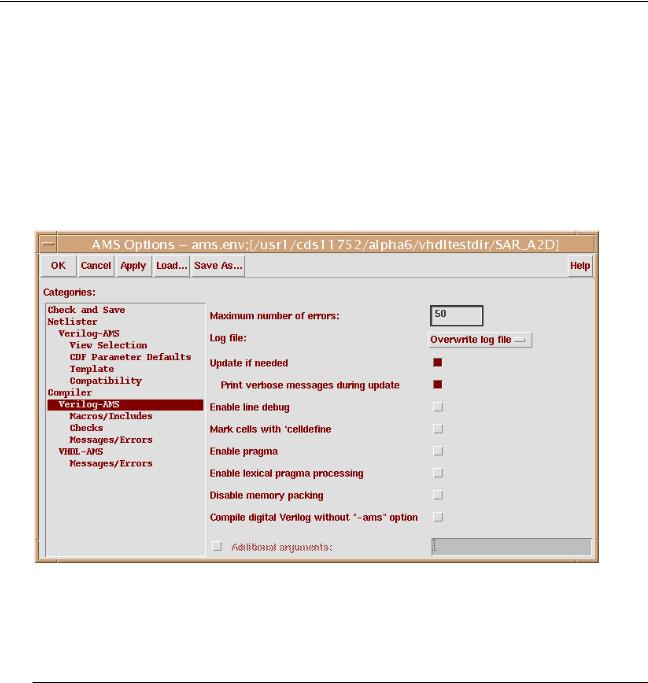

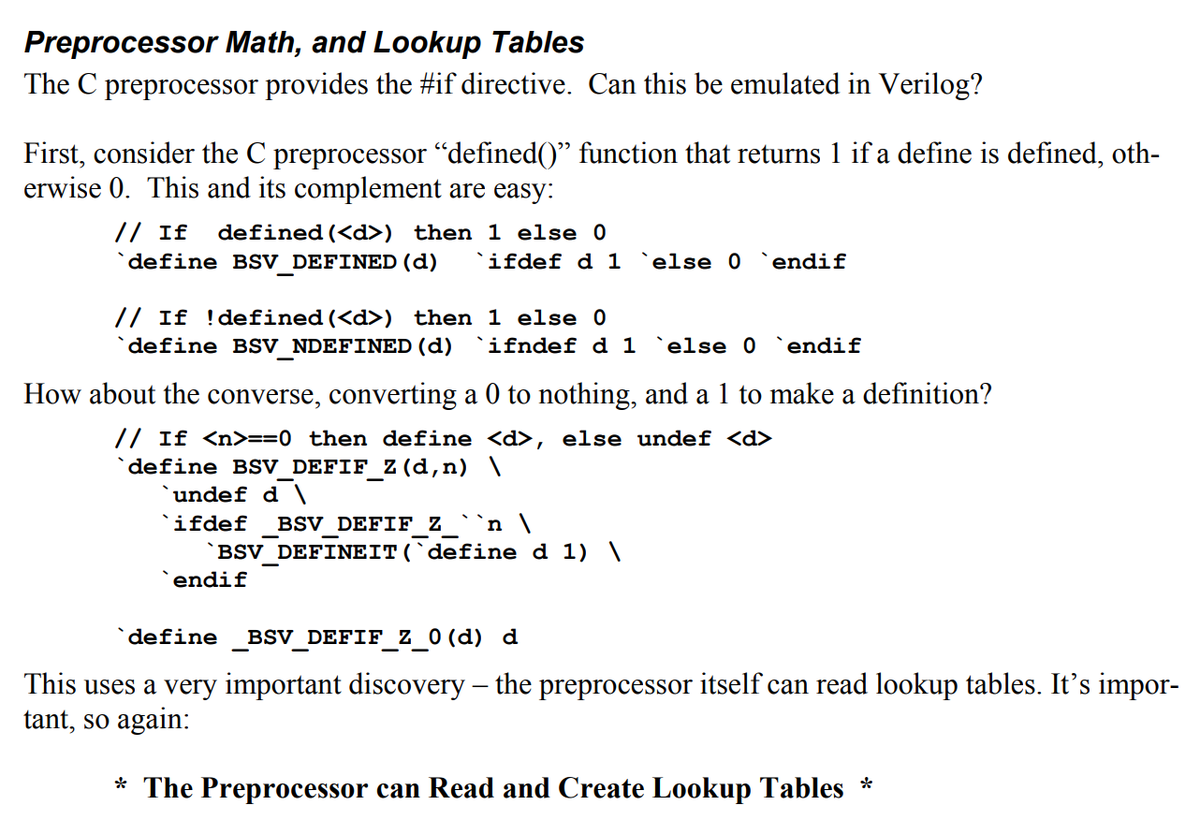

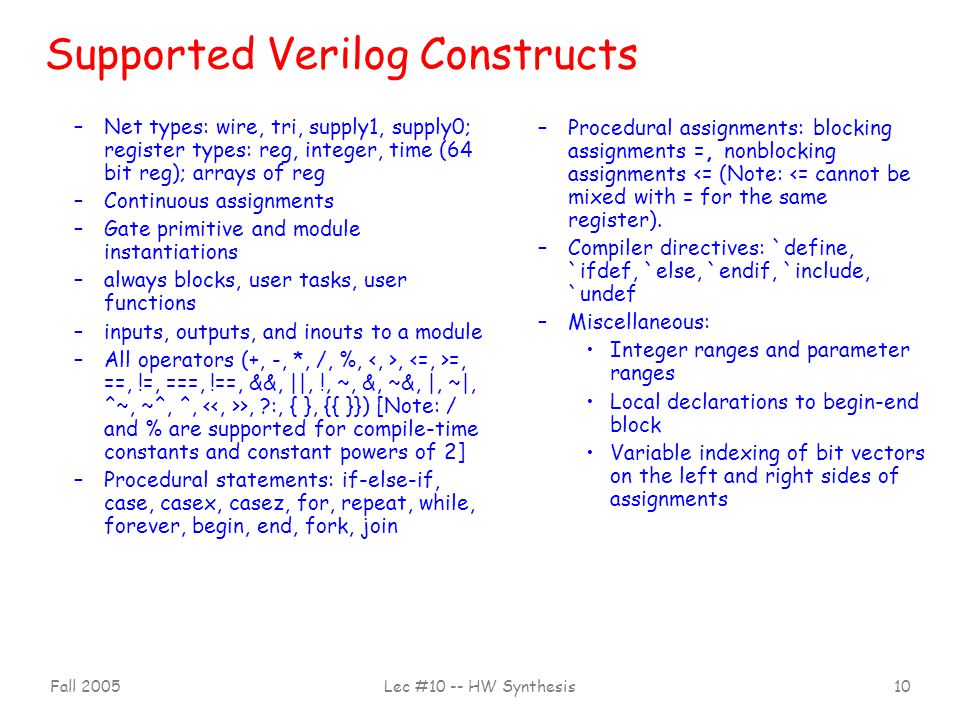

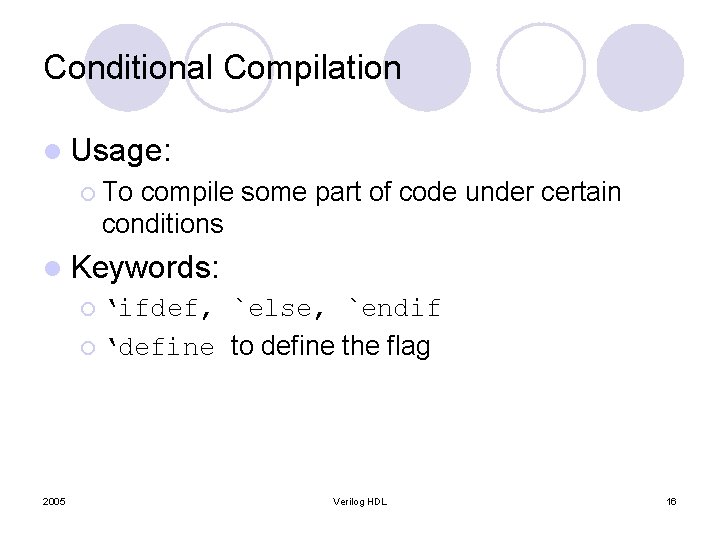

Furthermore, we tried to map Verilogdefined VDD/VSS and AVDD/AVSS nets to toplevel power/ground pins with globalNetConnect VDD type net net VDD verbose globalNetConnect VSS type net net VSS verbose etc The problem is that the mapping between Verilogdefined P/G nets is totally ignored (with the verbose option we see that actually no nets2 The #ifdef Directive The #ifdef directive has the following syntax #ifdef identifier newline This directive checks whether the identifier is currently defined Identifiers can be defined by a #define directive or on the command line If such identifiers have not been subsequently undefined, they are considered currently defined

Verilog ifdef parameter

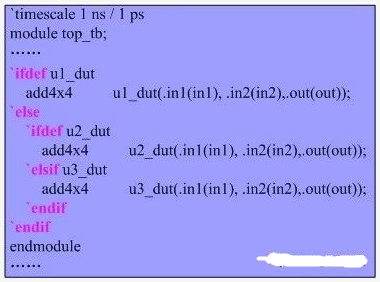

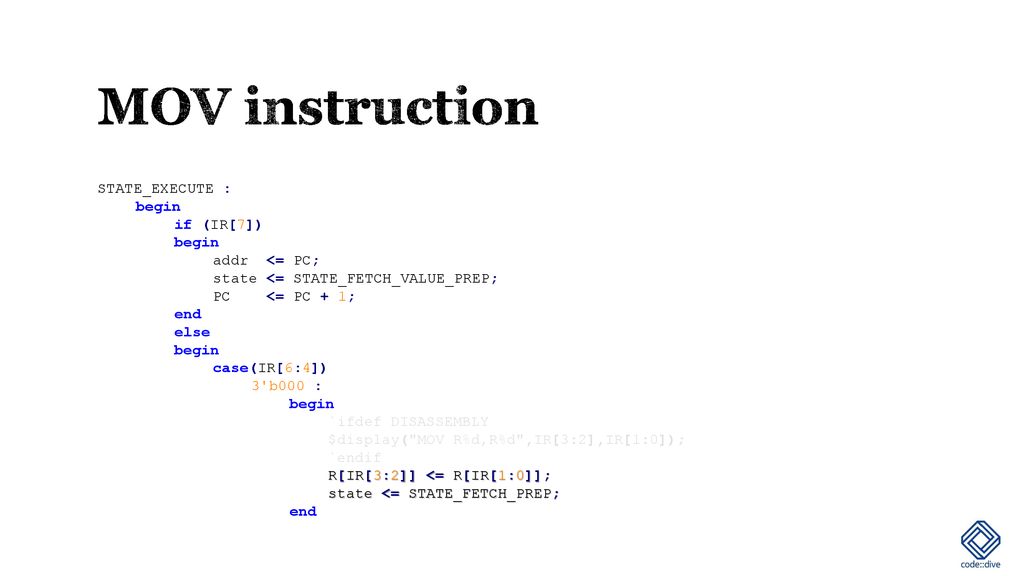

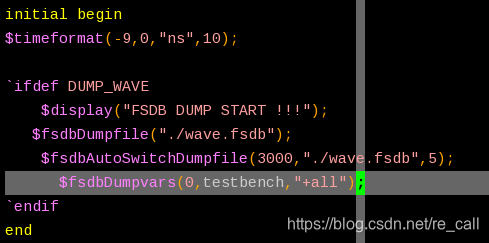

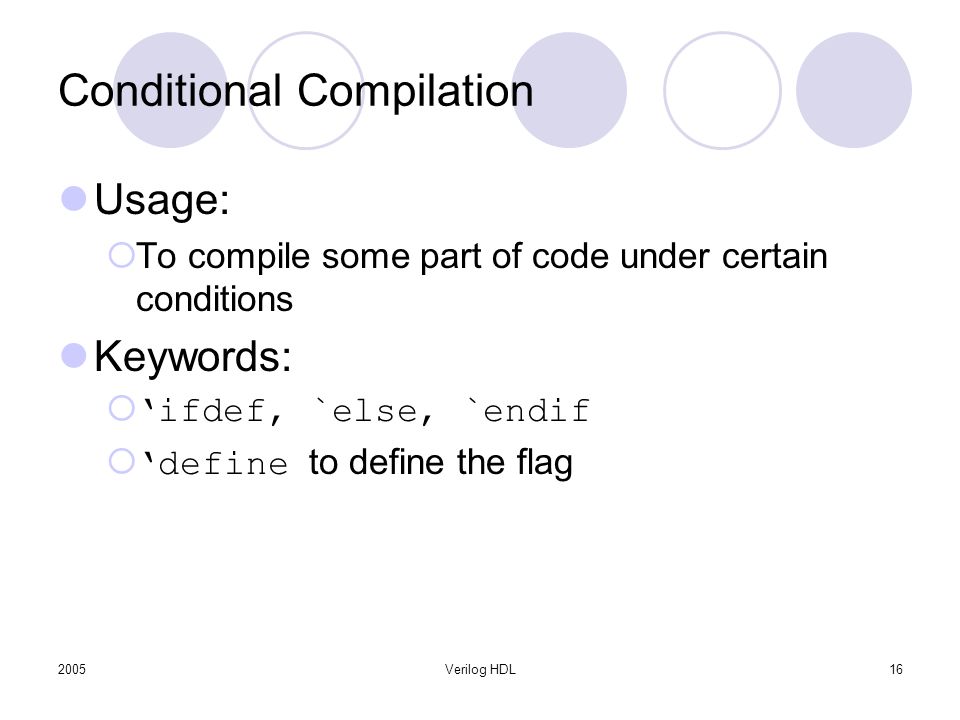

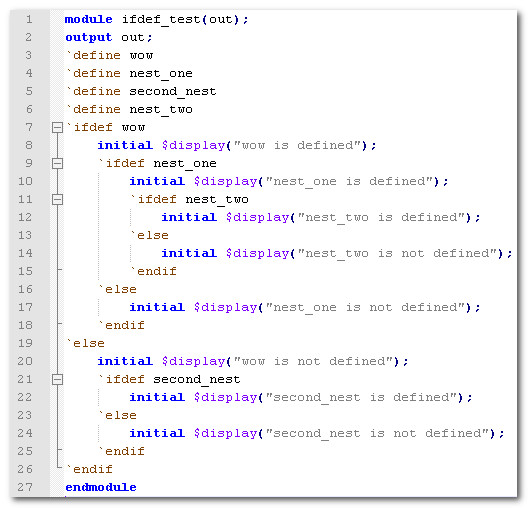

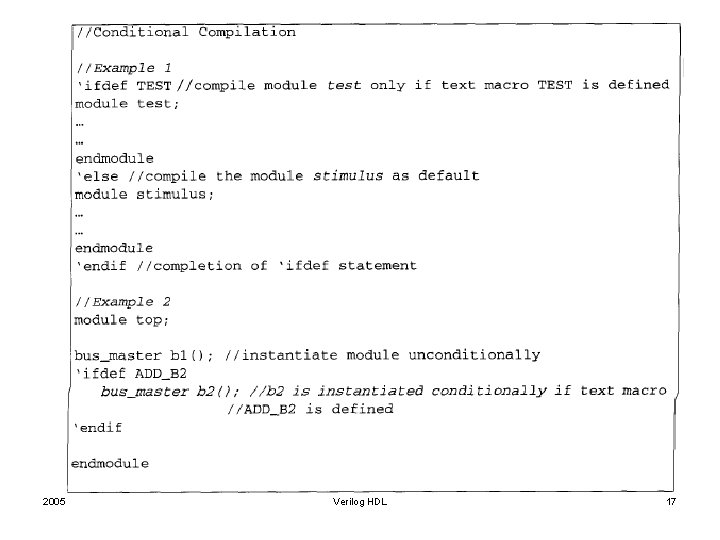

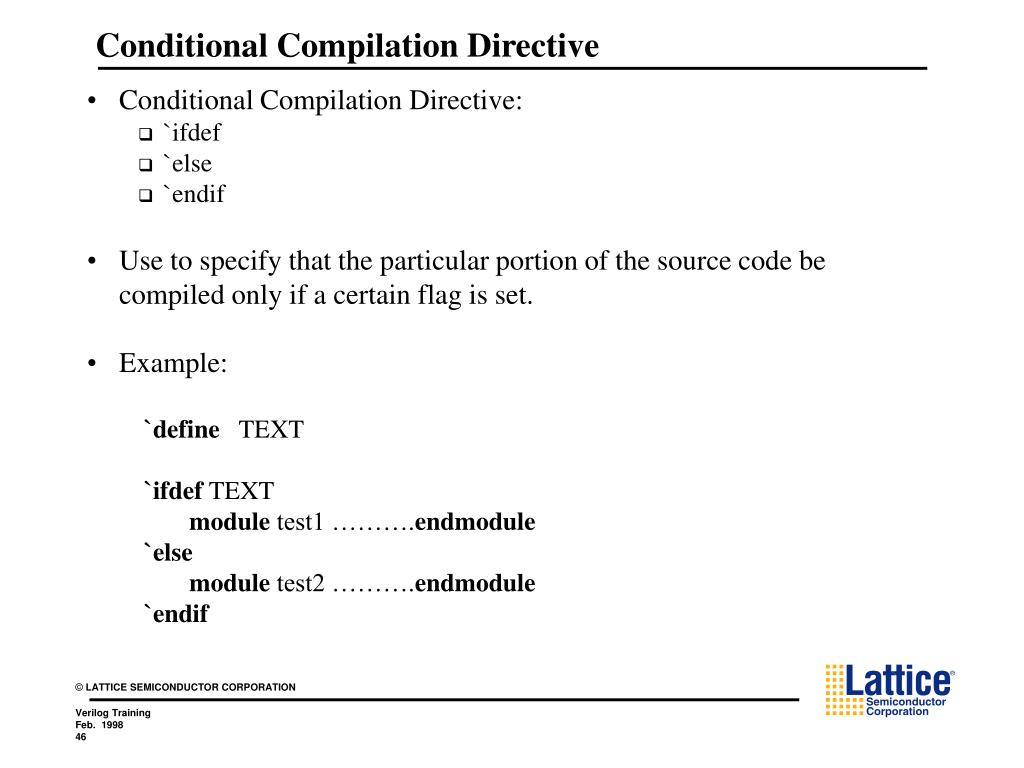

Verilog ifdef parameter- The `ifdef checks for the definition of a macro If it is defined, then the lines following the `ifdef are included If the macro is not defined and an `else directive exists then it includs what is following the `else The `ifndef compiler directive does the same as `ifdef but for when the macro is not defined`elsif D01 `ifdef D01 reg t040

Verilog系列 Ifdef和generate的差异 哔哩哔哩

Verilog `ifdef equivalent in VHDL?Conditional compilation can be achieved with Verilog `ifdef and `ifndef keywords These keywords can appear anywhere in the design and can be nested one inside the other The keyword `ifdef simply tells the compiler to include the piece of code until the next `else or `endif if the given macro called FLAG is defined using a `define directiveThe `ifdef compiler directive checks for the definition of a text_macro_name If the text_macro_name is defined, then the lines following the `ifdef directive are included If the text_macro_name is not defined and an `else directive exists, then this source is compiled The `ifndef compiler directive checks for the definition of a text_macro_name

Basic ConceptsDone 1Lexical conventions 21 Lexical tokens Syntax `ifdef macro_name `endif The macros can either be defined using ` define directive or be passed as a parameter with the compile command using the define option ` ifndef This directive is just the opposite of the ` ifdef directive This directive will compile the underlying code only when the macro is not definedHello, Is there any example of Verilog `ifdef equivalent in VHDL?

Verilog ifdef parameterのギャラリー

各画像をクリックすると、ダウンロードまたは拡大表示できます

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl | Integrating Systemc Models With Verilog Using Sutherland Hdl |

Integrating Systemc Models With Verilog Using Sutherland Hdl |  Integrating Systemc Models With Verilog Using Sutherland Hdl |

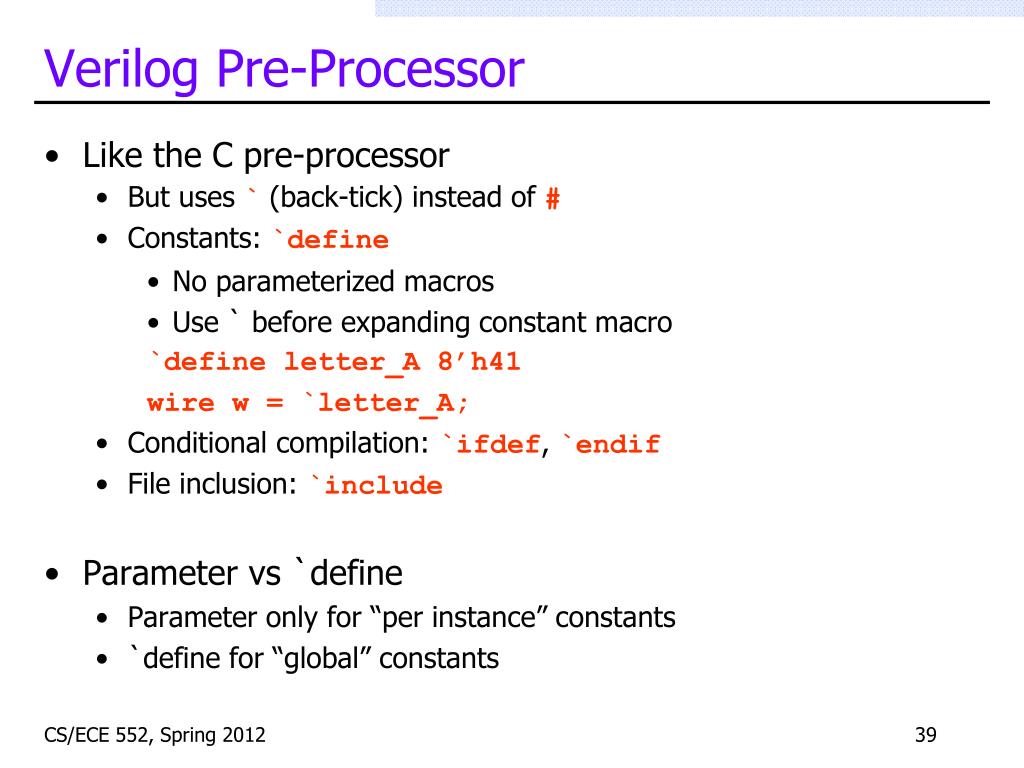

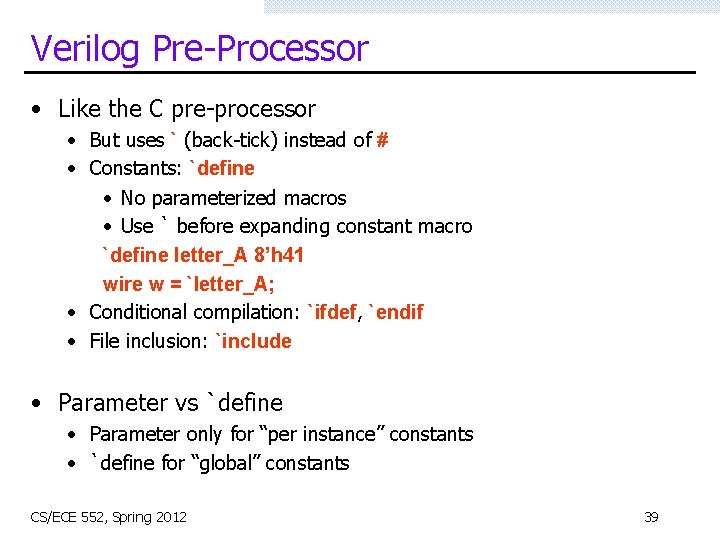

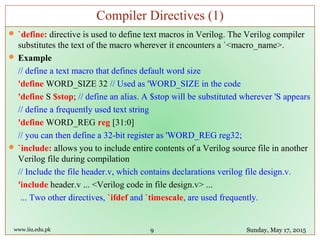

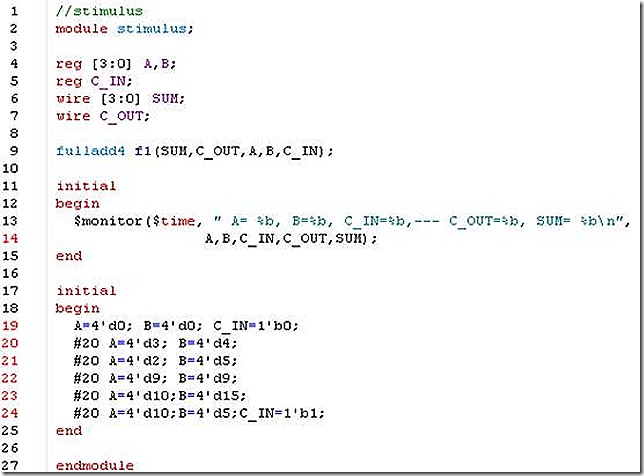

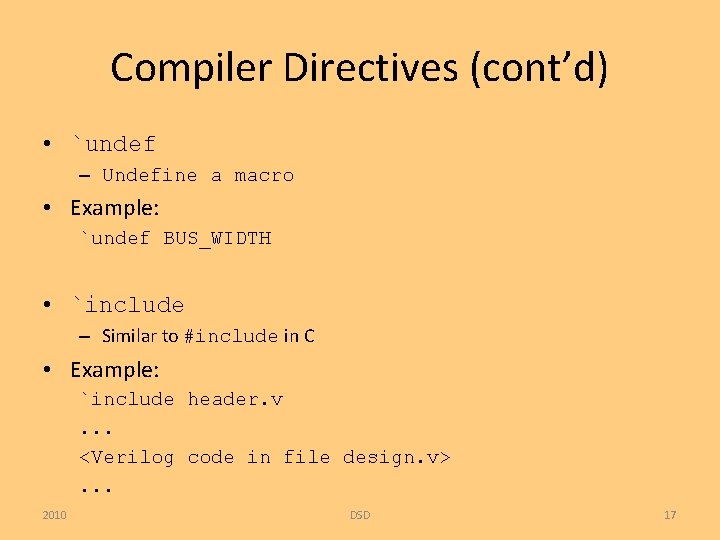

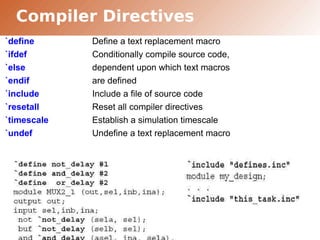

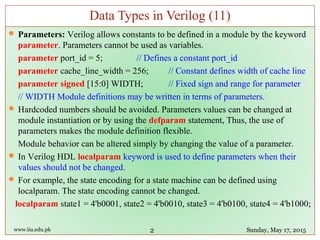

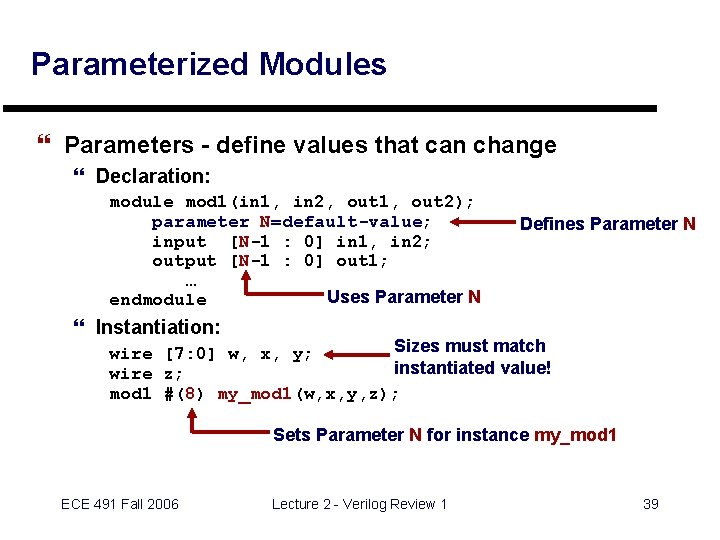

There are two ways to define constants parameter `define Parameter Parameters must be defined within module boundaries using the keyword parameter A parameter is a constant that is local to a module that can optionally be redefined on an instance Parameters are typically used to specify the width of variables and time delays Parameter exampleThese directives can be used to decide which lines of Verilog code should be included for the compilation (Example 4) The `ifdef directive checks if a macro name that follows this directive is defined If it is, then all lines between `ifdef and `else will be included Otherwise, only lines between `else and `endif will be compiled `include

Incoming Term: verilog ifdef and, verilog ifdef else, verilog ifdef multiple conditions, verilog ifdef parameter, verilog ifdef value, verilog ifdef simulation, verilog ifdef elsif else, verilog ifdef undef, verilog ifdef else if example, verilog ifdef ports,

0 件のコメント:

コメントを投稿